今日のワークロードのVLIWは単にひどい考えであるため、Itaniumは失敗しました。

広く尊敬されているコンピューター科学者のドナルド・クヌースは、2008年のインタビューで、「「Itanium」アプローチは非常に素晴らしいはずでした。希望のコンパイラーを作成することは基本的に不可能であることが判明するまでは」と述べました。

それはほとんど問題を釘付けにします。

基本ブロックごとに少なくとも数十の命令を取得する科学計算の場合、VLIWはおそらく正常に機能します。優れたバンドルを作成するための十分な手順があります。より最近のワークロードでは、基本ブロックごとに約6〜7の命令を取得することがよくありますが、それは単純に取得しません(SPEC2000の平均IIRCです)。コンパイラーは、バンドルに入れる独立した命令を見つけることができません。

Intel Atom(Silvermont以前)とAMD E-3 ** / 4 **を除いて、最新のx86プロセッサはすべて故障したプロセッサであると私は信じています。約100命令の動的命令ウィンドウを維持し、そのウィンドウ内で、入力の準備ができるたびに命令を実行します。複数の命令を実行する準備ができていて、それらがリソースをめぐって競合しない場合、それらは同じサイクルで一緒に実行されます。

では、これはVLIWとどう違うのですか?VLIWとアウトオブオーダーの最初の重要な違いは、アウトオブオーダープロセッサが異なる基本ブロックから命令を選択して同時に実行できることです。これらの命令はとにかく投機的に実行されます(主に分岐予測に基づいて)。2番目の重要な違いは、アウトオブオーダープロセッサがこれらのスケジュールを動的に決定することです(つまり、各動的命令は個別にスケジュールされます。VLIWコンパイラは静的命令で動作します)。

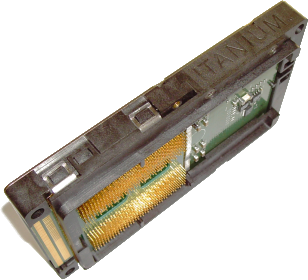

3番目の重要な違いは、命令セットを変更せずに、アウトオブオーダープロセッサの実装を必要なだけ広くできることです(Intel Coreには5つの実行ポートがあり、他のプロセッサには4つあります)。VLIWマシンは、一度に複数のバンドルを実行できます(競合しない場合)。たとえば、初期のItanium CPUは、クロックサイクルごとに最大2つのVLIWバンドル、6つの命令を実行し、後の設計(2011年のPoulson以降)を使用します。)最大4つのバンドルを実行=クロックあたり12命令、SMTは複数のスレッドからそれらの命令を取得します。その点で、実際のItaniumハードウェアは従来のインオーダースーパースカラー設計(P5 PentiumやAtomなど)に似ていますが、コンパイラーが命令レベルの並列性をハードウェアに公開するためのより多くの/より良い方法があります(理論的には、十分です、これが問題です)。

パフォーマンス面では、同様の仕様(キャッシュ、コアなど)で、Itaniumのがらくたを打ち負かしました。

では、なぜ今Itaniumを購入するのでしょうか。まあ、唯一の理由は本当にHP-UXです。HP-UXを実行したい場合は、それがその方法です...

多くのコンパイラライターはそれをこのように見ていません-彼らはItaniumが彼らにもっとやることを与え、彼らを制御に戻すなどの事実を常に気に入っていました。しかし彼らはそれがどれほど惨めに失敗したかを認めません。

脚注1:

これは、マルチコアプロセッサの価値に関する回答の一部でした。Knuthは、並列処理を利用するのは難しいと言っていました。VLIWのコンパイル時に、きめ細かい命令レベルの並列性(および明示的な推測:EPIC)を見つけて公開することも難しい問題であり、粗い並列性を見つけてシーケンシャルプログラムまたは関数を複数のスレッドに自動的に分割することに関連しています。複数のコアを活用します。

11年後、彼はまだ基本的に正しいです。スレッドごとのパフォーマンスは、ほとんどの非サーバーソフトウェアにとって依然として非常に重要であり、多くのコアが代替ではないため、CPUベンダーが注目しているものです。